ARM體系結構與編程(第2版) | 做自己 - 2024年7月

ARM體系結構與編程(第2版)

ARM處理器是一種16/32位的高性能、低成本、低功耗的嵌入式RISC微處理器,由ARM公司設計,然后授權給各半導體廠商生產,它目前已經成為應用最為廣泛的嵌入式處理器。共為分14章,對ARM處理器的體系結構、指令系統和開發工具進行了比較全面的介紹。其中包括ARM體系、ARM程序設計模型、ARM匯編語言程序設計、ARMC/C++語言程序設計、ARM連接器的使用、ARM集成開發環境CodeWarriorIDE的介紹及高性能的調試工具ADW的使用。並在此基礎上介紹一些典型的基於ARM體系的嵌入式應用系統設計的基本技術。

第1章 ARM概述及其基本編程模型1.1 ARM技術的應用領域及其特點1.2 ARM體系結構的版本及命名方法1.2.1 ARM體系結構的版本1.2.2 ARM體系的變種1.2.3 ARM/Thumb體系版本的命名格式1.3 ARM處理器系列1.3.1 ARM7系列1.3.2 ARM9系列1.3.3 ARM9E系列1.3.4 ARMl 0E系列1.3.5 SecurCore系列1.4 ARM處理器的運行模式1.5 ARM寄存器介紹1.5.1通用寄存器1.5.2程序狀態寄存器1.6 ARM體系的異常中斷1.6.1 ARM中異常中斷的種類1.6.2 ARM處理器對異常中斷的響應過程1.6.3從異常中斷處理程序中返回1.7 ARM體系中的存儲系統1.7.1 ARM體系中的存儲空間1.7.2 ARM存儲器格式1.7.3非對齊的存儲訪問操作1.7.4指令預取和自修改代碼第2章 ARM指令分類及其尋址方式2.1 ARM指令集概要介紹2.1.1 ARM指令的分類2.1.2 ARM指令的一般編碼格式2.1.3 ARM指令的條件碼域2.2 ARM指令的尋址方式2.2.1數據處理指令的操作數的尋址方式2.2.2字及無符號字節的Load/Store指令的尋址方式2.2.3雜類Load/Store指令的尋址方式2.2.4批量Load/Store指令的尋址方式2.2.5協處理器Load/Store指令的尋址方式第3章 ARM指令集介紹3.1 ARM指令集3.1.1跳轉指令3.1.2數據處理指令3.1.3乘法指令3.1.4雜類的算術指令3.1.5狀態寄存器訪問指令3.1.6 Load/Store內存訪問指令3.1.7批量Load/Store內存訪問指令3.1.8信號量操作指令3.1.9異常中斷產生指令3.1.10 ARM協處理器指令3.2一些基本的ARM指令功能段3.2.1算術邏輯運算指令的應用3.2.2跳轉指令的應用3.2.3 Load/Store指令的應用3.2.4批量Load/Store指令的應用3.2.5信號量指令的應用3.2.6與系統相關的一些指令代碼段3.3 Thumb指令介紹第4章 ARM匯編語言程序設計4.1偽操作4.1.1符號定義偽操作4.1.2數據定義偽操作4.1.3匯編控制偽操作4.1.4數據幀描述偽操作4.1.5信息報告偽操作4.1.6其他的偽操作4.2 ARM匯編語言偽指令4.3 ARM匯編語言語句的格式4.3.1 ARM匯編語言中的符號4.3.2 ARM匯編語言中的表達式4.4 ARM匯編語言程序的格式4.4.1匯編語言程序的格式4.4.2匯編語言子程序的調用4.5 ARM匯編編譯器的使用4.6匯編程序設計舉例4.6.1 ARM中偽操作的使用實例4.6.2 ARM匯編程序的實例第5章 ARM的存儲系統5.1 ARM存儲系統概述5.2 ARM中用於存儲管理的系統控制協處理器CP155.2.1訪問CP15寄存器的指令5.2.2 CP15中的寄存器5.3存儲器管理單元MMU5.3.1 存儲器管理單元MMU概述5.3.2禁止/使能MMU5.3.3 MMU中的地址變換過程5.3.4 MMU中的存儲訪問權限控制5.3.5 MMU中的域5.3.6關於快表的操作5.3.7 ARM中的存儲訪問失效5.4高速緩沖存儲器和寫緩沖區5.4.1基本概念5.4.2 Cache的工作原理和地址映像方法5.4.3 Cache的分類5.4.4 Cache的替換算法5.4.5緩沖技術的使用注意事項5.4.6存儲系統的一致性問題5.4.7 Cache內容鎖定5.4.8與Cache和寫緩沖區相關的編程接口5.5快速上下文切換技術5.5.1快速上下文切換技術原理5.5.2快速上下文切換技術編程接口5.6與存儲系統相關的程序設計指南5.6.1地址空間5.6.2存儲器的格式5.6.3非對齊的存儲訪問操作5.6.4指令預取和自修改代碼5.6.5 IMB5.6.6存儲器映射的I/O空間5.7 ARM存儲系統的實例5.7.1 L7205的存儲系統概述5.7.2 L7205中的SDRAM5.7.3 L7205中的MMU第6章 ATPCS介紹6.1 ATPCS概述6.2基本ATPCS6.2.1寄存器的使用規則6.2.2數據棧的使用規則6.2.3參數傳遞規則6.3幾種特定的ATPCS6.3.1 支持數據棧限制檢查的ATPCS6.3.2支持只讀段位置無關(ROPI)的ATPCS6.3.3支持可讀寫段位置無關(RWPI)的ATPCS6.3.4支持ARM程序和Thumb程序混合使用的ATPCS6.3.5處理浮點運算的ATPCS第7章 ARM程序和Thumb程序混合使用7.1概述7.2在匯編語言程序中通過用戶代碼支持interwork7.2.1可以實現程序狀態切換的指令7.2.2與程序狀態切換相關的偽操作7.2.3進行狀態切換的匯編程序實例7.3在C/C++程序中實現interwork7.4在匯編語言程序中通過連接器支持interwork7.4.1 利用veneers實現匯編程序間的程序狀態切換7.4.2利用veneers實現匯編程序與C/C++程序間的程序狀態切換第8章 C/C++以及匯編語言的混合編程8.1 內嵌匯編器的使用8.1.1 內嵌的匯編指令用法8.1.2內嵌的匯編器和armasm的區別8.1.3 在C/C++程序中使用內嵌的匯編指令8.1.4內嵌匯編指令的應用舉例8.2從匯編程序中訪問C程序變量8.3匯編程序、C程序以及C++程序的相互調用8.3.1在C++程序中使用C程序頭文件8.3.2匯編程序、C程序以及C++程序的相互調用舉例第9章 異常中斷處理9.1 ARM中的異常中斷處理概述9.1.1 ARM體系中的異常中斷種類9.1.2異常中斷向量表及異常中斷優先級9.1.3異常中斷使用的寄存器9.2進入和退出異常中斷的過程9.2.1 ARM處理器對異常中斷的響應過程9.2.2從異常中斷處理程序中返回9.3在應用程序中安排異常中斷處理程序9.3.1在系統復位時安排異常中斷處理程序9.3.2在C程序中安排異常中斷處理程序9.4 SWI異常中斷處理程序9.4.1 SWI異常中斷處理程序的實現9.4.2 SWI異常中斷調用9.5 FIQ和IRQ異常中斷處理程序9.5.1 IRQ/FIQ異常中斷處理程序9.5.2 IRQ異常中斷處理程序舉例9.6復位異常中斷處理程序9.7未定義指令異常中斷9.8指令預取中止異常中斷處理程序9.9數據訪問中止異常中斷處理程序第10章 ARM C/C++編譯器10.1 ARM C/C++編譯器概述10.1.1 ARM C/C++編譯器及語言庫介紹10.1.2 ARM編譯器中與搜索路徑相關的一些基本概念10.2 ARM編譯器命令行格式……第11章 ARM連接器第12章 嵌入式應用程序示例第13章 使用CodeWarrior第14章 ARM體系中的調試方法參考文獻

購置型保障性住房定價研究--以深圳...

購置型保障性住房定價研究--以深圳... 親子動手做/3D立體紙模型:夢幻公...

親子動手做/3D立體紙模型:夢幻公... 九歌少兒書房第65集:剪紙少女翩翩...

九歌少兒書房第65集:剪紙少女翩翩... 高輕型支擋技術及應用

高輕型支擋技術及應用 中國城市的可持續發展住宅政策與住宅...

中國城市的可持續發展住宅政策與住宅... 息賺秘笈

息賺秘笈 超可愛!小本廚房的手繪幸福餅乾 (...

超可愛!小本廚房的手繪幸福餅乾 (... 樓房花朵

樓房花朵 變革的基因(實踐篇):如何創新戰略...

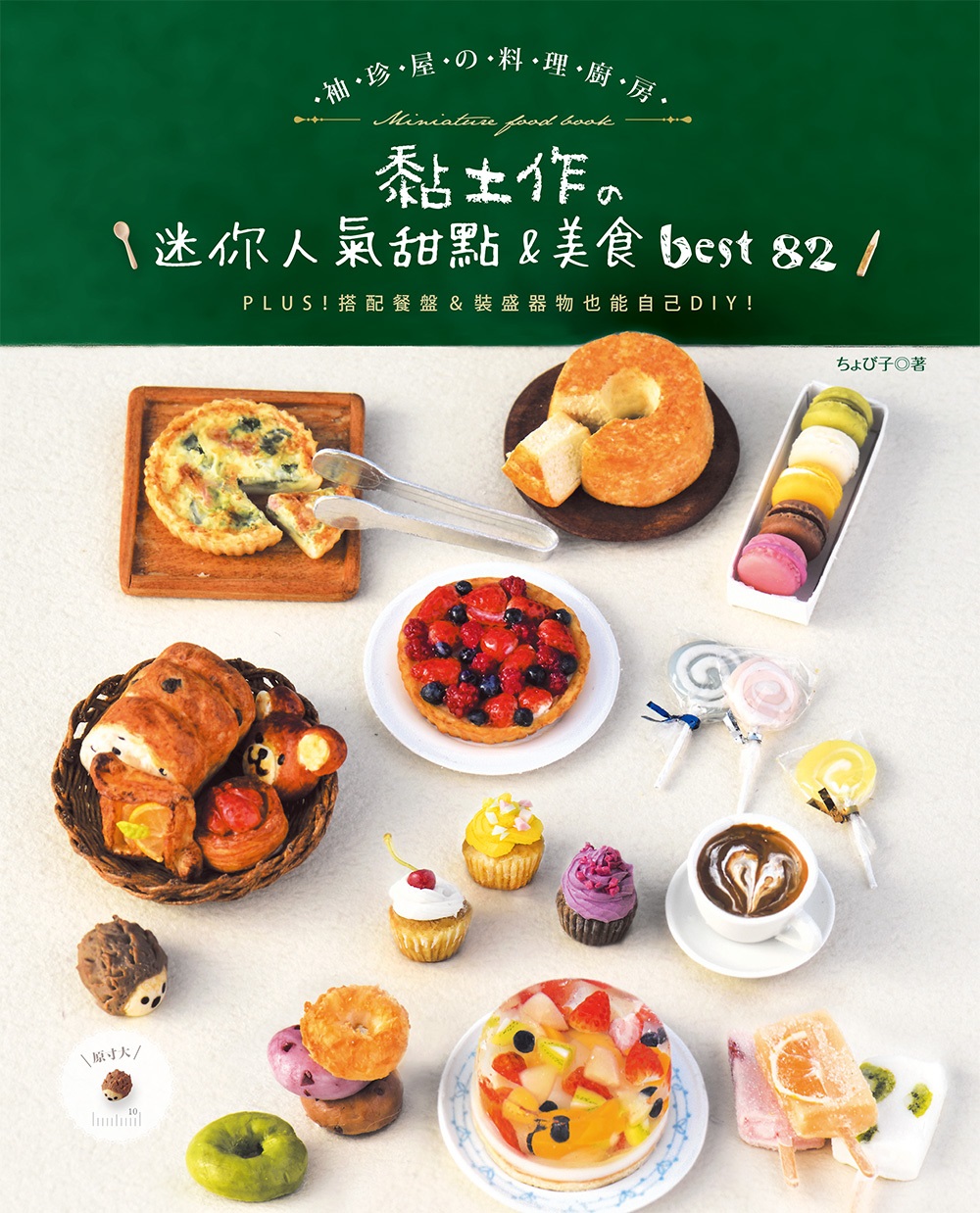

變革的基因(實踐篇):如何創新戰略... 袖珍屋的料理廚房:黏土作的迷你人氣...

袖珍屋的料理廚房:黏土作的迷你人氣...